関連商品・技術情報

商品基礎情報

PCIeにおける基準クロック(RefClk)の重要性

リファレンスクロック(RefClk)

リファレンスクロック(RefClk)

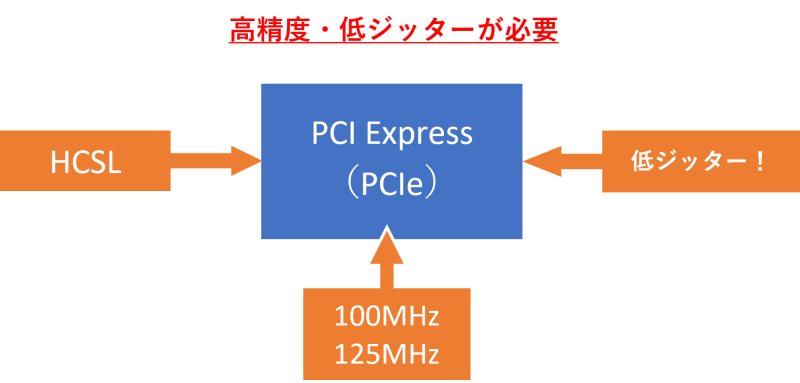

PCIeのような高速シリアル通信では、送信側と受信側がタイミングを正確に合わせる(同期する)必要があります。この同期の基準となるのが「リファレンスクロック(RefClk)」です。

役割: PCIeデバイスに共通のタイミング基準を提供し、データの送受信タイミングを正確に制御します。通常、100MHzもしくは125MHzの周波数が使用されます。

なぜ高精度な水晶デバイスが必要なのか?

PCIeの高速かつ安定した動作を実現するためには、極めて高精度で低ジッターなRefClkが不可欠です。この高品質なクロック信号を生成・供給するのが「水晶デバイス」です。

水晶発振器 (XO: Crystal Oscillator)

水晶振動子の持つ高い周波数安定性を利用して、正確なクロック信号を生成する電子部品です。PCIe向けには、特に以下の特性が求められます。

- 周波数: 基本的に100MHzもしくは125MHz

- 出力形式: HCSL (High-Speed Current Steering Logic) が標準的に用いられます。

- 低ジッター: ジッターはクロック周期の揺らぎであり、データ転送エラーの原因となります。PCIeの世代が上がる(高速化する)ほど、許容されるジッター量は厳しくなります。

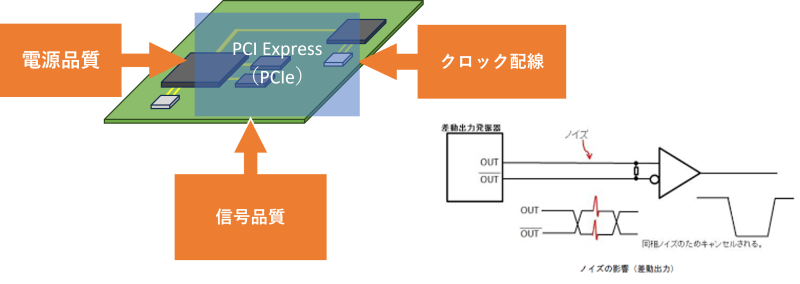

PCIe設計における注意点

高速なPCIeインターフェースを安定して動作させるためには、基板設計において細心の注意が必要です。

- 信号品質 (Signal Integrity):インピーダンス整合: 伝送路の特性インピーダンスを一定(通常85Ωまたは100Ω差動)に保ち、信号の反射を防ぐ。

- 損失: 信号が伝送路を通過する際の減衰を最小限に抑える。高周波になるほど損失は大きくなるため、低損失な基板材料の選定や配線長の最適化が重要。

- クロストーク: 隣接する信号線からのノイズ干渉を抑制する。配線間隔の確保やガードトレースの利用。

- クロック配線:差動配線: RefClkもデータ信号と同様に差動で配線し、ノイズ耐性を高める。

- 等長配線: 差動ペアの2本の線の長さを厳密に合わせ、スキューを最小限にする。

- ノイズ対策: 電源プレーンからのノイズや他の信号線からの干渉を避けるため、配線経路やビア配置に注意する。

- 電源品質 (Power Integrity):高速なスイッチング動作を支えるためには、低ノイズで安定した電源供給が不可欠。デカップリングコンデンサの適切な配置などが重要。

PCIeと水晶デバイスの未来

PCI Expressは、コンピューターシステムの性能向上に不可欠な、進化し続ける高速インターフェースです。その転送速度は世代を重ねるごとに倍増しており、Gen6、Gen7といった更なる高速化が進行中です。

この驚異的な高速データ転送を、低いエラーレートで安定して実現するためには、**高精度かつ低ジッターな基準クロック(RefClk)**が絶対に必要です。そして、その重要な役割を担っているのが、水晶発振器(XO)やクロックジェネレーターといった水晶デバイスです。

私たちエレクトロニクス商社は、最新のPCIe規格に対応した高性能な水晶デバイスをはじめ、お客様の製品開発に貢献する最適な電子部品をご提案してまいります。PCIeや水晶デバイスに関するご質問、ご要望がございましたら、お気軽にお問い合わせください。

EPSON水晶製品のラインアップのご紹介

100MHJz、125MHzでHCSL信号でのEPSON製品ラインアップはこちらから!