Napatech : クラウド、通信、エンタープライズ向けSmartNIC & IPUソリューション

商品基礎情報

なぜNapatechが必要なのか?

現代のデータセンターや通信ネットワークは、トラフィックの爆発的な増加とセキュリティ要件の高度化に直面しています。ネットワーク処理に汎用CPUのリソースを消費してしまうと、本来のアプリケーションに割くべき計算能力が失われてしまいます。

Napatechのハードウェアとソフトウェアを組み合わせたソリューションは、CPUの負荷を劇的に軽減(オフロード)し、パケットロスゼロの完全なトラフィック可視化と超低遅延処理を実現します。これにより、インフラのTCO(総所有コスト)を削減し、投資対効果(ROI)を最大化します。

主要ハードウェア製品ラインアップ

業界標準のサーバーにシームレスに統合できるよう設計された、FPGAベースの高性能SmartNICおよびDPU/IPUのラインナップです。通信、クラウド、エンタープライズの多様な要件に合わせて、最適なパフォーマンスを提供します。

各製品の特長

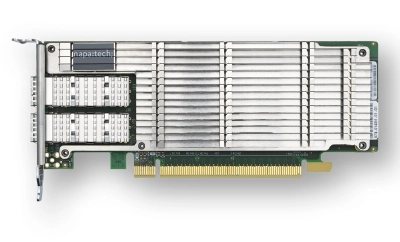

NT400D13 PCIe4 SmartNIC

NT400D13 PCIe4 SmartNIC

- NT400D13 SmartNIC

最大200 Gbpsのネットワークデータをパケットロスゼロでフルキャプチャ可能な最先端のSmartNICです。PCIe Gen4 x16をサポートし、ネットワークポートとサーバーメモリ間で最大220 Gbpsの全二重パケット転送を実現します。

NT400D11 SmartNIC

NT400D11 SmartNIC

- NT400D11 SmartNIC

最大200 Gbpsのトラフィックロスゼロキャプチャを提供するPCIe Gen4対応SmartNICです。Intel Agilex FPGAを搭載し、高負荷なアプリケーションにおいてCPUコアの効率的な活用と高度なインフラストラクチャ処理のオフロードを可能にします。

NT200A02-SCC SmartNIC

NT200A02-SCC SmartNIC

- NT200A02 SmartNIC

100 Gbpsの持続的なトラフィックや200 Gbpsのトラフィックバーストをパケットロスゼロでキャプチャします。1Uサーバーで2x100Gや2x40G等の構成を可能にし、最大1億4,000万フローのステートフル処理をサポートします。

NT100A01-SCC SmartNIC

NT100A01-SCC SmartNIC

- NT100A01 SmartNIC

100 Gbpsネットワークデータのロスゼロフルキャプチャを提供するSmartNICです。4つの10/25Gポートを備え、最大9,000万フローのステートフル処理に対応することで、Suricataなどの高負荷なセキュリティアプリケーションの最適化に貢献します。

NT50B01 SmartNIC

NT50B01 SmartNIC

- NT50B01 SmartNIC

省スペースなハーフハイト(ロープロファイル)設計でありながら、50 Gbpsのロスゼロキャプチャを提供するSmartNICです。厳しい通信業界基準(NEBS Level 3)に準拠しており、エッジや通信インフラの仮想化環境に最適です。

NT40A11-SCC SmartNIC

NT40A11-SCC SmartNIC

- NT40A11 SmartNIC

40 Gbpsネットワークデータのロスゼロフルキャプチャを提供します。4x10Gまたは4x1G構成に対応し、最大36,000フローのステートレスフロー処理による高度なフィルタリングやスライシングでサーバーの負荷を軽減します。

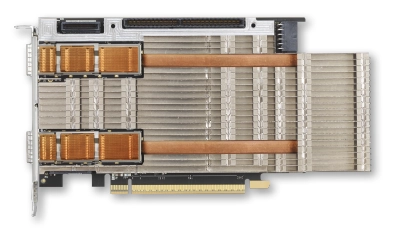

F3076X 400G DPU

F3076X 400G DPU

- F3076X DPU (Data Processing Unit)

Intel Xeon 6 SoC(32コア)とIntel Agilex FPGAを搭載した強力なPCIe Gen5対応DPUです。400Gパイプラインをサポートし、AIインフラや分散ストレージ、セキュリティオフロードなど、高度な処理要件にボトルネックなしで対応します。

F3070X 400G DPU

F3070X 400G DPU

- N3070X SmartNIC

400G PCIe Gen5に対応し、Intel Agilex FPGAを搭載した高性能SmartNICです。AIインフラや5G、クラウドコンピューティングにおけるネットワークおよびセキュリティデータプレーンの完全なオフロードとアクセラレーションを提供します。

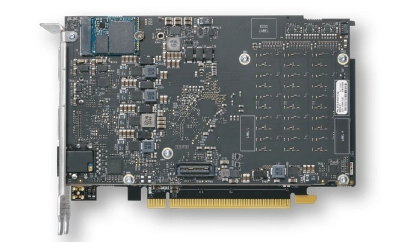

F2070X DPU

F2070X DPU

- F2070X IPU (Infrastructure Processing Unit)

Intel Xeon D SoC(8コア)とIntel Agilex FPGAを1枚のPCIe Gen4カードに統合したIPU/DPUです。テナント分離を伴う仮想化クラウドやベアメタルサーバーにおいて、ネットワーク、ストレージ、セキュリティの高度なオフロードを実現します。

ハードウェア スペック・マトリクス

| 製品名 | フォームファクタ | 搭載プロセッサ | ネットワークポート | 対応リンクスピード | ホストIF | 冷却方式 |

| NT400D13 | フルハイト、3/4 または ハーフレングス | Intel Agilex AGFB022 FPGA | 2 × QSFP56 | 10G, 25G, 40G, 100G, 200G | PCIe Gen4 x16 | アクティブ / パッシブ |

| NT400D11 | フルハイト、 ハーフレングス |

Intel Agilex AGF 014 FPGA | 2 × QSFP56 | 10G, 25G, 40G, 100G | PCIe Gen4 x16 | アクティブ / パッシブ |

| NT200A02 | フルハイト、 ハーフレングス |

Xilinx XCVU5P FPGA | 2 × QSFP28 | 1G, 10G, 25G, 40G, 100G | PCIe Gen3 x16 | アクティブ / パッシブ |

| NT100A01 | フルハイト、 ハーフレングス |

Xilinx XCVU5P FPGA | 4 × SFP28 | 1G, 10G, 25G | PCIe Gen3 x16 | アクティブ / パッシブ |

| NT50B01 | ハーフハイト、 ハーフレングス |

Xilinx XCKU15P FPGA | 2 × SFP28 | 1G, 10G, 25G | PCIe Gen3 x16 | パッシブ |

| NT40A11 | フルハイト、 ハーフレングス |

Xilinx KU11P FPGA | 4 × SFP+ | 1G, 10G | PCIe Gen3 x8 | アクティブ / パッシブ |

| F3076X | フルハイト、3/4レングス (2スロット) | Intel Agilex AGIC041 &Intel Xeon 6532P-B | 2 × QSFP-DD | 10G, 25G, 40G, 50G, 100G, 200G, 400G | PCIe Gen5 x16 | パッシブ |

| N3070X | フルハイト、1/2 または 3/4レングス | Intel Agilex AGIC041 | 2 × QSFP-DD | 100G, 200G, 400G | PCIe Gen5 x16 | パッシブ |

| F2070X | フルハイト、ハーフレングス (2スロット) | Intel Agilex AGFC023 &Intel Xeon D-1736 | 2 × QSFP28/56 | 10G, 25G, 100G | PCIe Gen4 x16 | パッシブ |

目的別に最適化された Link™ ソフトウェアスイート

NapatechのSmartNICおよびIPU/DPUは、強力なハードウェアと専用のソフトウェアモジュール「Link™ ソフトウェアスイート」を組み合わせることで、特定のユースケースにおいてシステムレベルで最高クラスのパフォーマンスを発揮します。以下は、各モジュールの詳細な特長です。

Link-Capture™(パケットキャプチャ&リプレイ)

ネットワーク監視、テスト、セキュリティ分析において「100%の可視性」を提供する、パケットロスゼロのキャプチャおよびリプレイ・ソフトウェアです。

- 完全な可視性とロスゼロ処理: すべてのパケットサイズにおいて、最大200 Gbpsの双方向トラフィックをいかなる条件下でもロスゼロでキャプチャします。

- ナノ秒精度のタイムスタンプ: 受信したすべてのイーサネットフレームに1ナノ秒(ns)精度のタイムスタンプを付与。複数ポートからのパケットを時系列順に正確にマージし、WiresharkやSuricata、Zeekなどの分析ツールの性能を最大3倍以上に引き上げます。

- 高度なフロー管理と負荷分散: 最大1億8,500万の双方向フローをステートフルに管理し、関連するトラフィックを特定のCPUコアにインテリジェントに分散(最大128のRx/Txキュー)させます。

- データ削減機能: ハードウェアレベルでの重複排除(最大99.99%の重複パケットを検出・破棄)、パケットスライシング(ペイロードの切り捨て)、機密データのマスキングをサポートし、ストレージ容量と分析負荷を大幅に削減します。

Link-Inline™(インライン処理アクセラレーション)

ネットワークおよびセキュリティアプリケーションのデータプレーンをオフロードし、インバウンドおよびアウトバウンドの高速インライン処理を実現します。

- ステートフル・フロー処理: 1億以上のフローテーブルエントリをサポートし、毎秒200万以上のフローのセットアップとティアダウンを低遅延で実行します。

- 5G UPFの完全オフロード: 通信事業者向けに、5GコアのUPF(ユーザープレーン機能)データパスをSmartNICにオフロード。GTPのカプセル化・非カプセル化などをハードウェアで処理し、サーバーあたりの収容ユーザー数を大幅に最大化します。

- 動的なルール適用: 既知のフローに対するアクション(ドロップ、ファストフォワードなど)をSmartNIC上で完結させ、未知のパケットのみをホストCPUに渡すことで、アプリケーションのCPU消費を劇的に削減します。

Link-Virtualization™(仮想化・OVSオフロード)

クラウドやエッジデータセンターにおける仮想スイッチの処理負荷をハードウェアに肩代わりさせ、テナント(VMやコンテナ)に提供できるCPUコアを解放します。

- OVSの圧倒的な高速化: Open vSwitch(OVS)のデータプレーンを完全にオフロード。標準的なOVSカーネル実装と比較して最大60倍のパフォーマンス向上を実現し、CPU消費を最大90%削減します。

- 高スループット: 最大100Gbpsのスイッチングスループットと、最大6,000万pps(パケット/秒)の仮想アプリケーション向けデータ配信をサポートします。

- 標準技術との統合: VirtIO 1.1(vDPA対応)やライブマイグレーションをサポートし、OpenStackなどのクラウドオーケストレーション環境にシームレスに統合できます。さらに、CPUを消費せずにVM間のトラフィックをミラーリングする監視機能も備えています。

Link-Storage™(NVMe/TCP ストレージオフロード)

Intel® IPU(F2070X等)向けに設計され、分散ストレージアクセスに伴う複雑なネットワーク処理をオフロードします。

- NVMe over TCPの完全オフロード: ホストCPUに代わってIPU側でNVMe/TCPイニシエータを実行。2x100Gのスループット環境において、10マイクロ秒未満の遅延で600万 IOPS(4KBブロック)という驚異的なストレージ性能を実現します。

- 標準ドライバの互換性: ホスト側には16のブロックデバイス(Virtio-Blk)として認識されるため、主要なLinuxディストリビューションに標準搭載されているVirtIO-Blockドライバがそのまま利用可能で、独自のソフトウェアは不要です。

- エアギャップ・セキュリティ: ストレージ通信のネットワークインターフェースをホストCPUから完全に隠蔽(分離)することで、サイバー攻撃からストレージインフラを保護します。

Link-Security™(セキュリティ&暗号化オフロード)

IPUを活用し、データセンター内の通信セキュリティ(暗号化・復号化)処理によるCPUのボトルネックを解消します。

- TLSの高速オフロード: 計算負荷の高いTLS 1.2 / 1.3プロトコルの暗号化および復号化、ならびにTCP処理(TSO, GRO, LROなど)をIPUに完全オフロードします。

- インフラとテナントの分離: ホストCPU(テナント領域)とIPU間でゼロトラストの分離レイヤーを構築。テナント側からの攻撃でインフラサービスが侵害されるリスクを排除します。

- リバースプロキシとWeb高速化: NginxベースのHTTP(s)リバースプロキシ機能によるTLS暗号化レイヤーの追加や、静的ファイルのキャッシュ、画像最適化によるWebサーバーの応答時間短縮も提供します。

Link-Programmable™(カスタムFPGA開発環境)

特定の独自要件やプロトコルを持つOEMやエンドユーザー向けに、Napatechの堅牢なハードウェア上で独自のFPGA IPを展開できる開発キットです。

- 柔軟なプログラミング: 高水準言語である「P4」や、よりきめ細かな制御が可能な「VHDL」を利用して、カスタムパケット処理パイプラインを構築できます。

- 豊富なリファレンスと統合ツール: パケットの解析、フィルタリング、フロー分類などの基本ブロックがサンプルコードとして提供され、DPDK、Linux、Windows環境に統合するためのAPIやドライバも完備されています。

- HFTや独自プロトコルに最適: マイクロ秒を争う金融の高頻度取引(HFT)システムや、防衛・研究機関における実験的な独自プロトコル処理など、極限のカスタマイズが求められる環境に最適です。

対象業界と詳細ユースケース

Napatechのソリューションは、数マイクロ秒の遅延削減が求められる金融業界から、莫大なトラフィックを処理する通信キャリアまで、幅広いミッションクリティカルな現場で採用されています。

●金融・高頻度取引 (HFT) およびアルゴリズム取引

市場の優位性を保つために「Tick-to-Trade(相場データの受信から発注までの時間)」の短縮と、規制遵守のための正確な記録が不可欠です。

- AI推論の超低遅延化: CPUでは処理が追いつかないAIモデル(XGBoostやLightGBMなど)による自動取引判断をSmartNICにオフロード。パートナー企業(XeleraやMyrtle.ai)との統合ソリューションにより、1.55〜5.1マイクロ秒という驚異的な超低遅延での推論を実現しました。

- 遅延の90%削減: ある大手ティア1投資銀行のケースでは、NapatechのSmartNICを用いた分析プラットフォームを導入することで、Tick-to-Tradeレイテンシを100マイクロ秒から10マイクロ秒へと90%削減することに成功しています。

●通信オペレーター・5Gネットワーク

5Gの普及に伴い、ネットワーク処理の負荷がサーバーCPUを圧迫しています。

- 5G UPFの完全オフロード: 5Gコアネットワークで最も処理負荷の高い「ユーザープレーン機能(UPF)」をSmartNICにオフロード。これにより、標準的なNICを使用した場合と比較して、サーバーあたりの収容ユーザー数を7倍に最大化し、CAPEX(設備投資)とOPEX(運用コスト)を80%以上削減した実証結果があります。

- VoLTE/VoWiFiの品質保証: ナノ秒精度のタイムスタンプと独自の相関メカニズム(パケットへのフィンガープリント付与)により、ネットワーク内のあらゆるポイントでの遅延を正確に測定。大規模で高価な専用測定器を、低コストな標準サーバー構成で置き換えることに成功しました。

●サイバーセキュリティとネットワーク監視

100G、200G、さらに400Gへと高速化するネットワークにおいて、脅威を見逃さない「完全な可視性」を提供します。

- ロスゼロのパケットキャプチャ: Suricata、Snort、Zeekなどのオープンソース・セキュリティツールの性能を最大化。CPU負荷をほぼゼロに抑えながらフルラインレートでパケットをキャプチャし、サーバーの必要台数を1/3に削減します。

- パフォーマンスの倍増: IBM QRadar SIEMの導入事例では、SmartNICによる高度なトラフィックのロードバランシング(負荷分散)機能を活用し、ソフトウェアに変更を加えることなくアプリケーションの処理性能を2倍に向上させました。

- コンプライアンス対応: NEOX Networksとの事例では、400G環境において重複排除や個人情報部分のパケットマスキングをハードウェアで実行し、ストレージ容量の節約と厳格なプライバシー規制(GDPR等)への準拠を同時に達成しています。

●クラウド・データセンター

インフラストラクチャ処理(仮想スイッチ、ストレージ、セキュリティ)によるCPUリソースの消費をなくし、収益を生む仮想マシン(VM)用のCPUコアを解放します。

- ソフトウェア圧縮のボトルネック解消: Nokiaのストレージアプリケーションの事例では、CPUによるソフトウェア圧縮をFPGAでのハードウェア圧縮に置き換えることで、圧縮時間を1/30に短縮し、40倍のパフォーマンス向上を実現。40コア必要だった処理をわずか1コアに削減し、約400万ドルのコスト削減効果を実証しました。

- テナントの分離とセキュリティ: F2070X IPUは、ホストCPU(テナント領域)とインフラ処理(通信やストレージ)を物理的に分離(エアギャップ)。テナント側からのサイバー攻撃によってインフラ側が乗っ取られるリスクを排除し、クラウド事業者に安全でスケーラブルな基盤を提供します。