複製不可能な「シリコン指紋」.SRAM PUF搭載 Secure-FPGA「GW1NSER」

GowinのSecure-FPGA「GW1NSERシリーズ」は、FPGAの柔軟性、Arm Cortex-M3 MCUの処理能力、そして高度なセキュリティ機能を1チップに統合した革新的なデバイスです。ここでは、その特徴とSecure機能を内蔵するメリットおよびアプリケーション例をご紹介します。

Gowin Secure-FPGA (GW1NSER) 概要

主な特長

GowinのSecure-FPGA「GW1NSERシリーズ」最大の特長は、

SRAM PUF(Physical Unclonable Function:物理的複製不可能な関数)技術を基盤としたハードウェアを搭載している点です。

これにより、秘密鍵をデバイス内に一切保存する必要がなく、物理的な攻撃や複製に対して極めて高い耐性を持ちます。セキュアブート、デバイス認証、データの暗号化・復号といった機能を、小型かつ低コストなワンチップで実現できます。

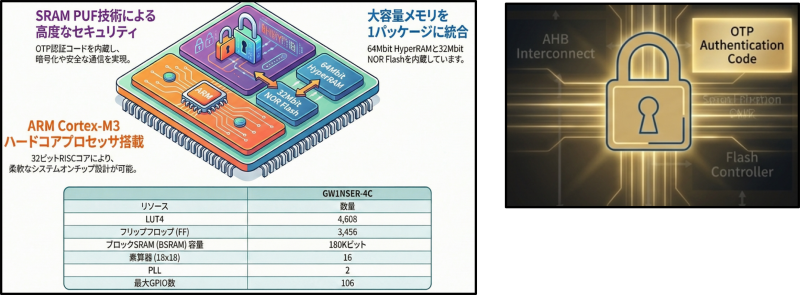

GW1NSERはSRAM PUF技術をベースとしたハードウェアレベルのセキュリティを基盤に、マイクロプロセッサ、FPGAファブリック、大容量メモリを統合した、セキュアなシステムインパッケージ(SiP)です。

GW1NSERのセキュリティは、ソフトウェア暗号化よりも強固なハードウェア固有の物理特性に基づいています。

「SRAM PUF(Physically Unclonable Function)」とは:

- 製造プロセスに起因するSRAMセルの微細な個体差を利用して、チップごとに固有の「デジタル指紋」を生成する技術。

- この「指紋」は物理的なものであり外部から読み出したり別のチップに複製したりすることは原理的に不可能です。

※SRAM PUFの詳細につきましては、下記「関連製品・技術情報」を参照ください。

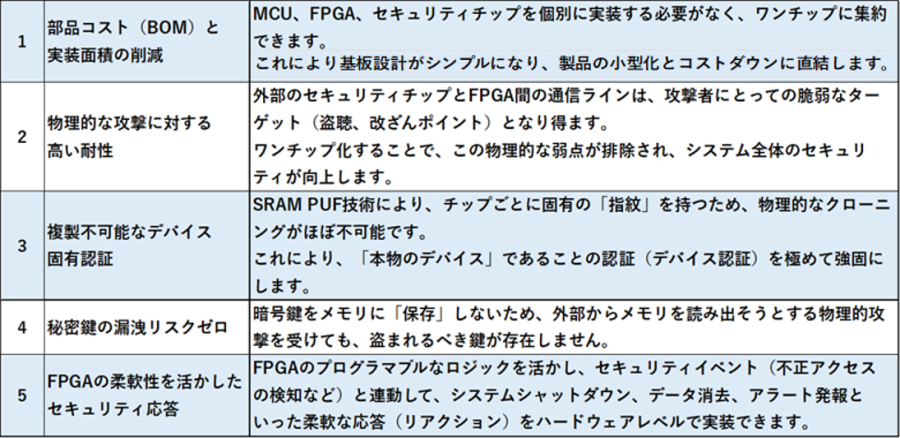

FPGAにSecure機能を内蔵するメリット

FPGAにPUFのような高度なセキュリティ機能を内蔵することには、従来の「FPGA + 外部セキュリティチップ」という構成にはない、以下のような大きなメリットがあります。

SRAM PUF:微細な製造誤差から生まれる、世界最高レベルのセキュリティ鍵

「SRAM PUF(Physically Unclonable Function)」とは

- 製造プロセスに起因するSRAMセルの微細な個体差を利用して、チップごとに固有の「デジタル指紋」を生成する技術です。

- この「指紋」は物理的なものであり外部から読み出したり別のチップに複製したりすることは原理的に不可能です。

Gowin Secure-FPGA (GW1NSER) 技術概要

1.ハイブリッド・プロセッシング・コア

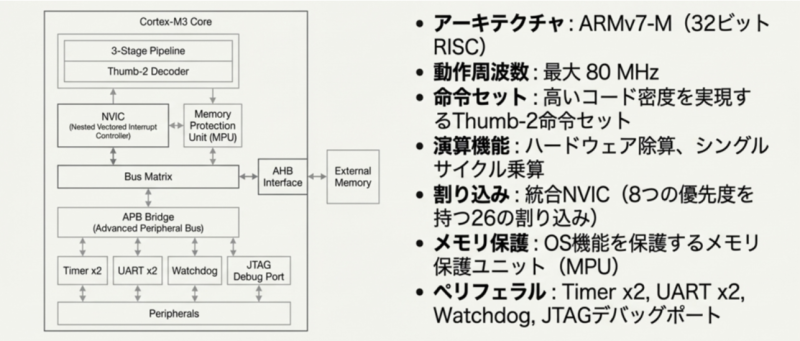

(1)ARM Cortex-M3プロセッサ

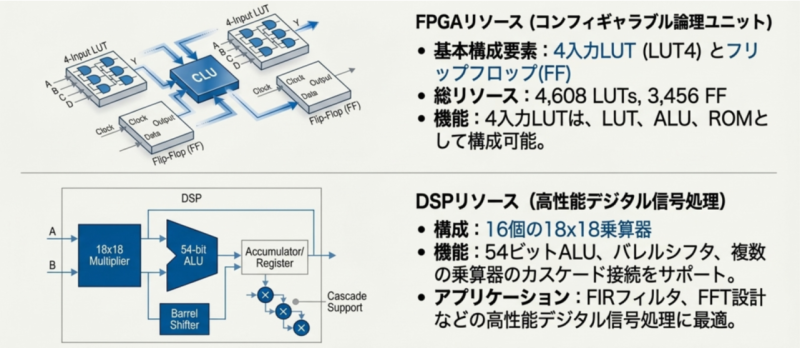

(2)FPGAファブリックとDSPリソース

2.統合メモリサブシステム

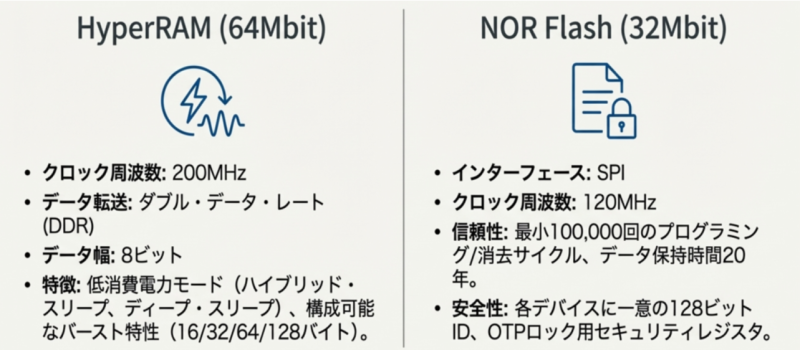

(1)大容量HyperRAMとNOR Flash

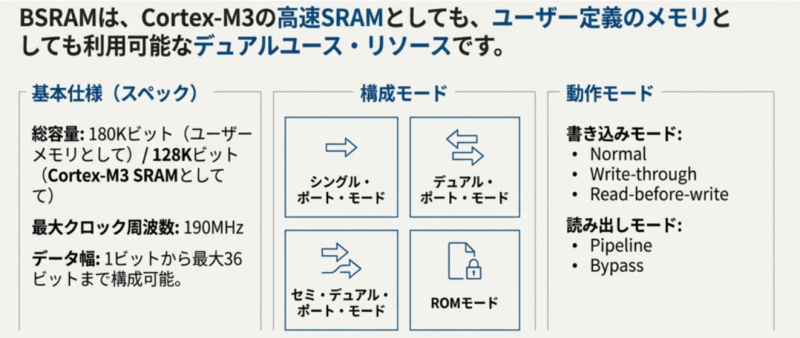

(2)柔軟なオンチップBSRAM

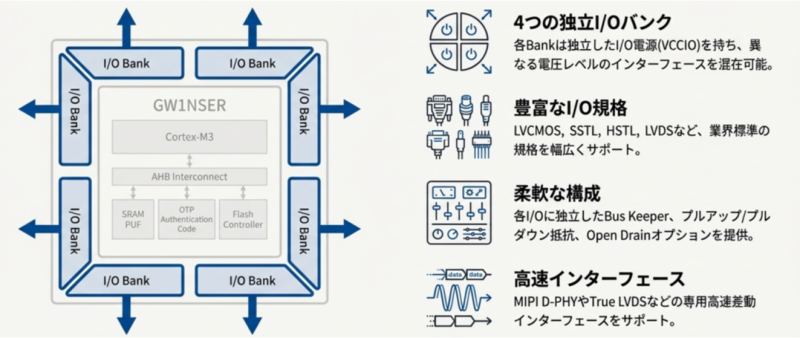

3.高性能・多用途I/O

(1)外部と接続できる彩なインターフェイス

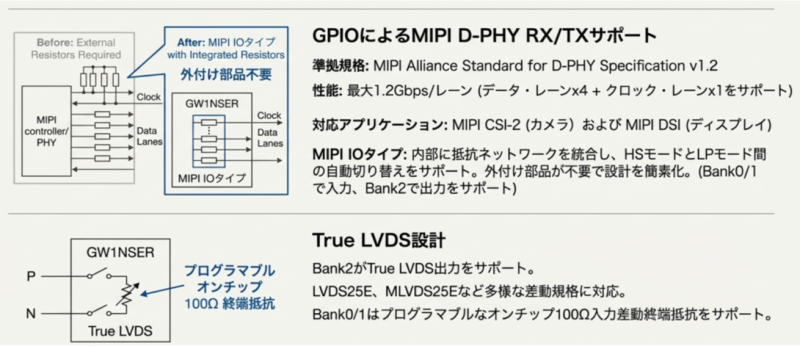

(2)MIPI D-PHYとTrue LVDS高速I/O

5.まとめ

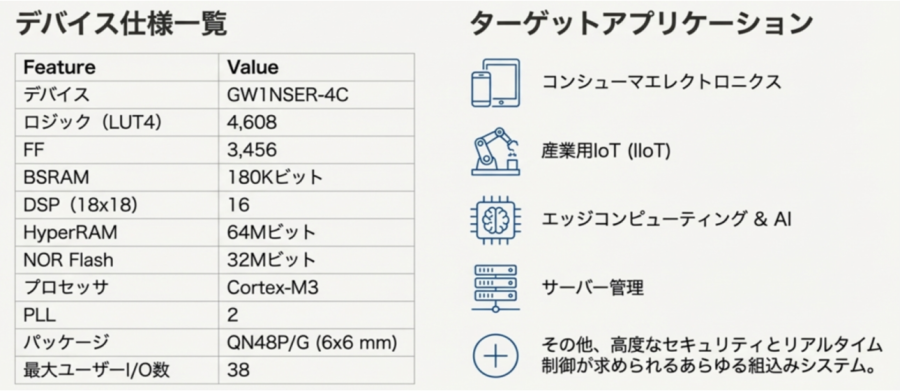

GW1NSER-4C:仕様とアプリケーション概要