スイッチング電源の問題について [リンギング対策 コンデンサ編]

【スイッチング電源の問題について [リンギング対策 レイアウト編]】では、基板の層(レイヤ)数の違いによるリンギング対策を行い、効果を確認しました。今回は寄生インダクタンスを小さくする対策を行った効果を説明します。

リンギングの原因について

寄生インダクタンスについて

電流が生じると、それに合わせて磁場が発生します。

このことによりパターンがインダクタの役割を持ってしまいます。

これが寄生インダクタンスの正体です。

パターンが長くなればそれだけ寄生インダクタンスが増えます。

リンギングについて

下図は、寄生インダクタンスと寄生容量を含めた等価回路図です。

灰色で示した箇所が寄生成分です。

IC内部のFETに含まれている寄生容量については対策することができません。

そこで、寄生インダクタンスについて対策してみます。

寄生インダクタンスを減らすには

寄生インダクタンスの対策について

寄生インダクタンスはパターンが長くなることによって生じるため、入力コンデンサとFETのループ(水色)を短くする必要があります。下図は入力コンデンサを可能な限り近づけた際のイメージ回路図です。

測定内容

どうすればリンギングを削減できるのか調べるために EV2333H-TL-00A を参考に基板を作成しました。

測定項目

- リンギング

EV2333H-TL-00Aの回路図は以下の通りです。

レイアウト

下図右側は入力コンデンサを移動した基板のレイアウトです。

実際にレイアウトを作成する際は下記のようにすることで、入力ピンとGNDピンのループを短くすることができます。

今回は変更前のループ長が約10mmに対して変更後のループ長を3mmに変更しました。

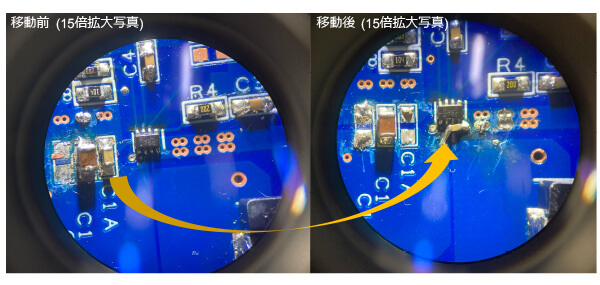

実装写真

矢印の位置にコンデンサ(C1A)を移動しました。

Vin-GND間が最短となるようにSWノード上を跨ぐようにしてコンデンサで接続しています。

コンデンサを移動した2層基板をオリジナルレイアウト③、4層基板をオリジナルレイアウト④とします。

測定環境

以下の測定環境で評価を行います。

実際の測定の様子

SWノードにリンギング測定用のビアを設けています。

測定結果

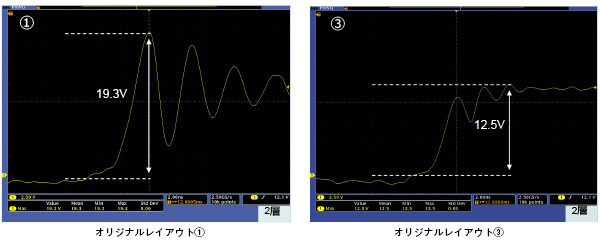

オリジナルレイアウト③(2層基板)の測定結果

2層基板のリンギングを測定したところ、最大で12.5Vになりました。

測定結果の比較

左上の数字はレイアウトの種類を表しています。

ベースとなる2層基板のオリジナルレイアウト①から、入力コンデンサの位置を変更したオリジナルレイアウト③のVin-GND間のループを短くすることでリンギングを減らすことができました。

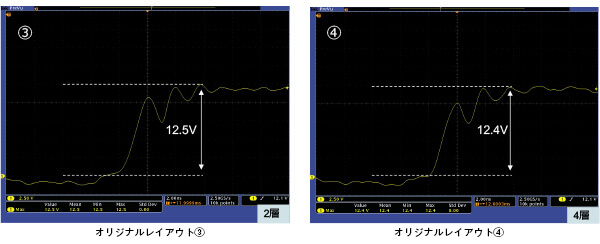

オリジナルレイアウト④(4層基板)の測定結果

4層基板のリンギングを測定したところ、最大で12.4Vになりました。

測定結果の比較

2層基板であっても4層基板と同程度のリンギングにすることができました。

まとめ

下記に結果をまとめた表を記載します。

結果からコンデンサを追加することでリンギングのピーク値を抑えることが確認できました。

全体のまとめ

下記に結果をまとめた表を記載します。

結果から入力コンデンサを可能な限り近づけることで、2層基板であっても少ないリンギングを実現することができています。

今回は層数を増やすよりも入力コンデンサを近づけることが対策として効果的でした。

レイアウト名の数字は測定結果の波形に記載した数字と同じです。

担当エンジニアからの一言

SW電源を使用する際にリンギングについて気にされる方も多いと思います。

今回作成したレイアウトでは、入力コンデンサを入力ピンの近傍に配置することで、

リンギングを大幅に減らすことができました。

このことから、寄生インダクタンスを減らすことがリンギング対策で重要であることが分かります。

今回コンデンサを近づけることで2層と4層の違いがあまり見られませんでした。

これは2層基板でも入力コンデンサを入力ピンの近傍に配置することで、リンギングを大幅に減らすことができたのでベタグランドの追加による効果がほとんど見られなかったからだと考えます。

そのため、まずは入力コンデンサと入力ピンの距離が最短になるようレイアウトを作成することを推奨します。