GOWIN EDA DSim Studio InstallからSimulationまで‒ 補足資料

GOWINセミコンダクター社のFPGA統合開発環境“GOWIN EDA”の論理Simulatorとして、Altair Engineering社の“DSim Studio”が採用されました。

ここでは「DSim Studio InstallからSimulationまで」で紹介している内容について説明しきれなかった、Visual Studio CodeへのDSim Studio Install後のフロー、Project Folder設定の詳細、GOWIN Primitive Libraryの登録方法、遅延Simulationの方法などを掲載しています。

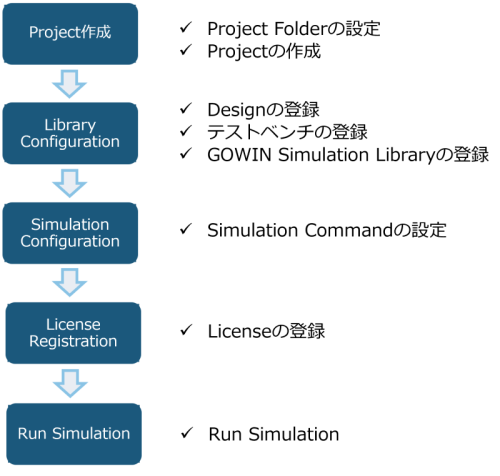

Visual Studio CodeへのDSim Studio Install後のフロー

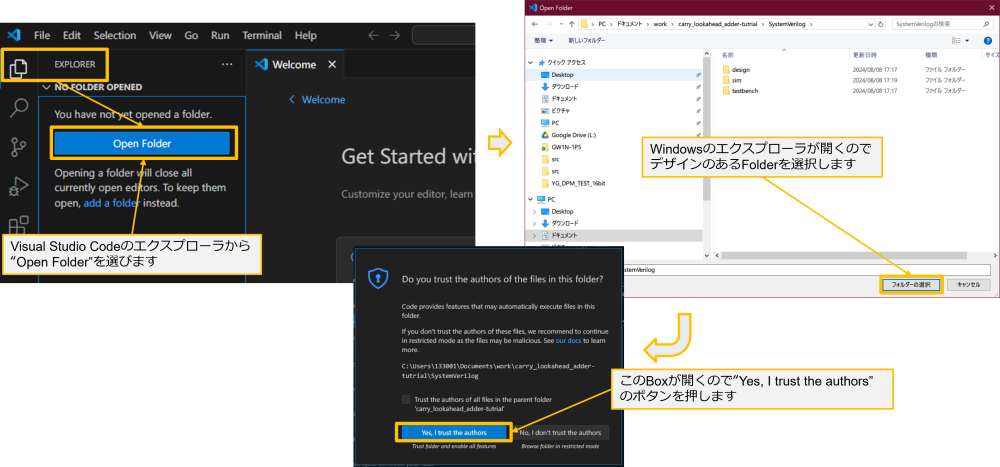

Project Folderの設定

Project Folderの設定 - 1

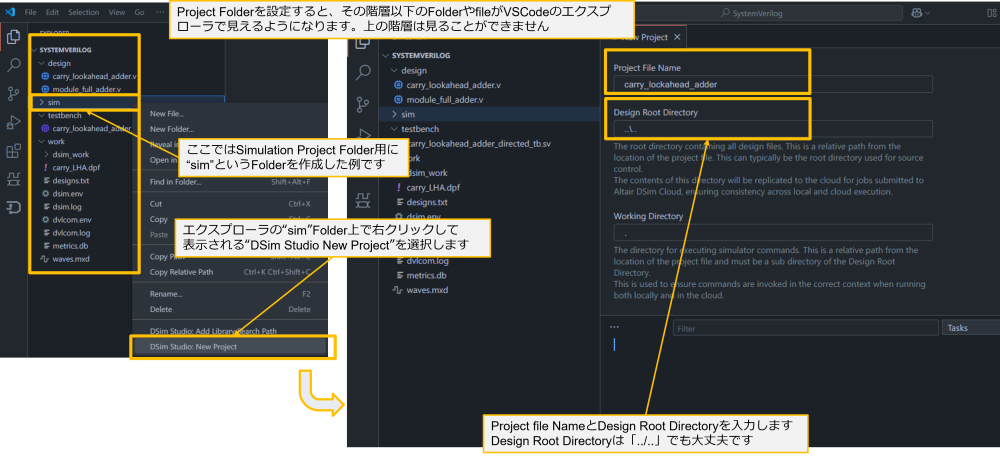

Project Folderの設定 - 2

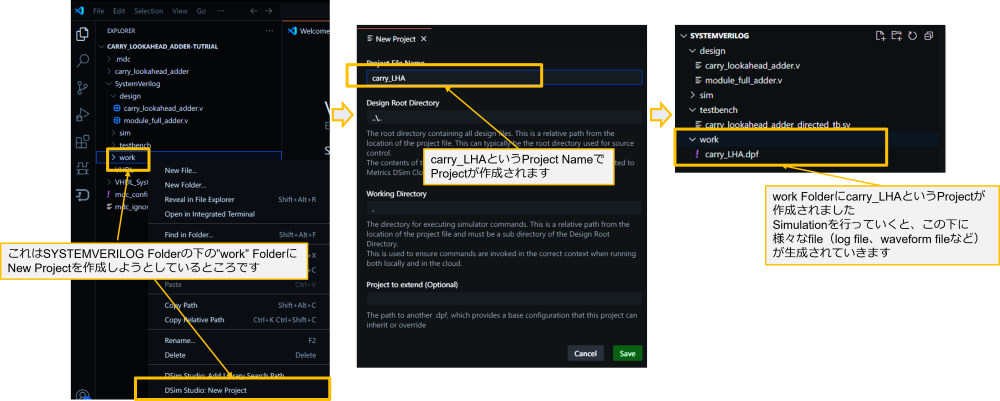

Project Folderの設定 - 3

Visual Studio Codeのエクスプローラ上では、選択したFolder以下が見えている状態なので、その階層にSimulation用work Folderを用意するとその後の作業が容易になります。

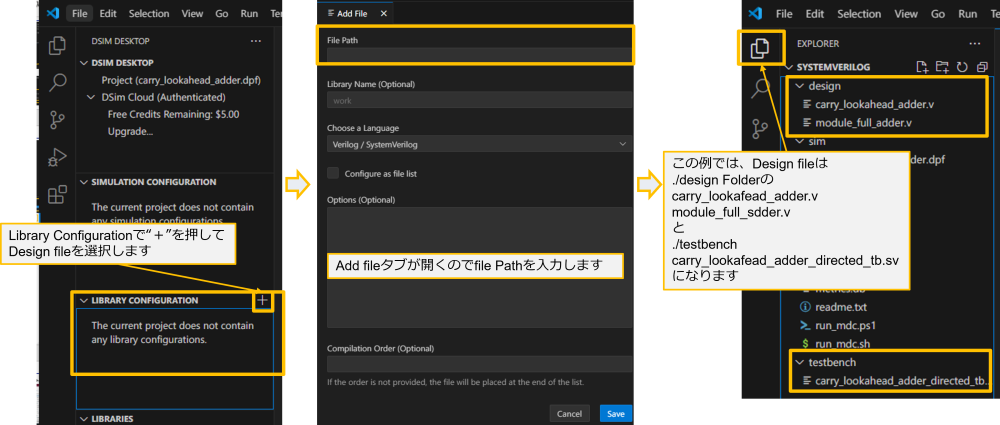

Library Configuration

Library ConfigurationではSimulationに必要なDesign fileの登録を行います

Design fileの登録方法は以下の2通りです

①個別登録

②一括登録

SystemVerilog、Verilogは拡張子にて自動判断

- SystemVerilog Assertionを利用したVerification 機能を利用している場合、拡張子が「**.v」だとCompileでErrorになります。

Designの登録方法① - 個別登録

Simulation用Design fileをそれぞれ登録します。

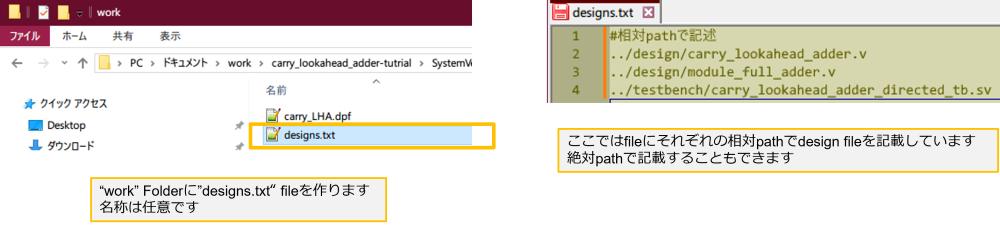

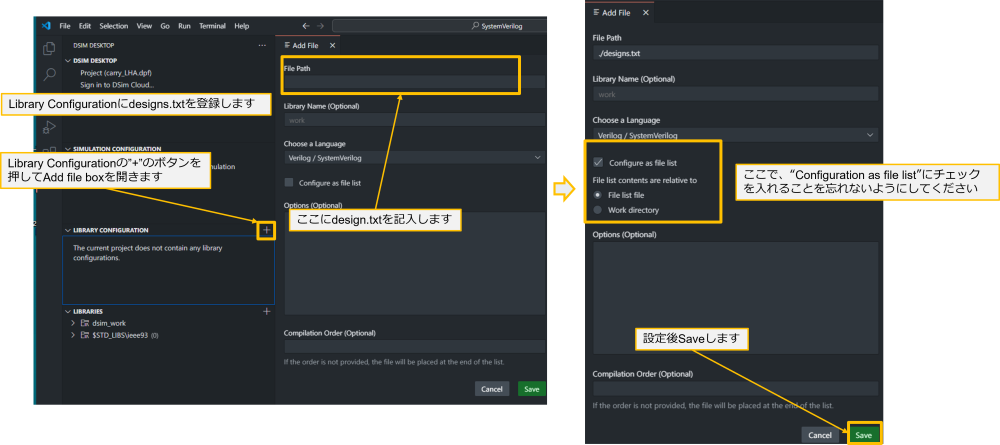

Designの登録方法② - 一括登録

一括登録は必要なDesign file(designs.v/designs.vhd等)をあらかじめfileに記載しておく方法で、Design fileが多いProjectではこちらの方が便利です。

Designの登録方法② - 一括登録

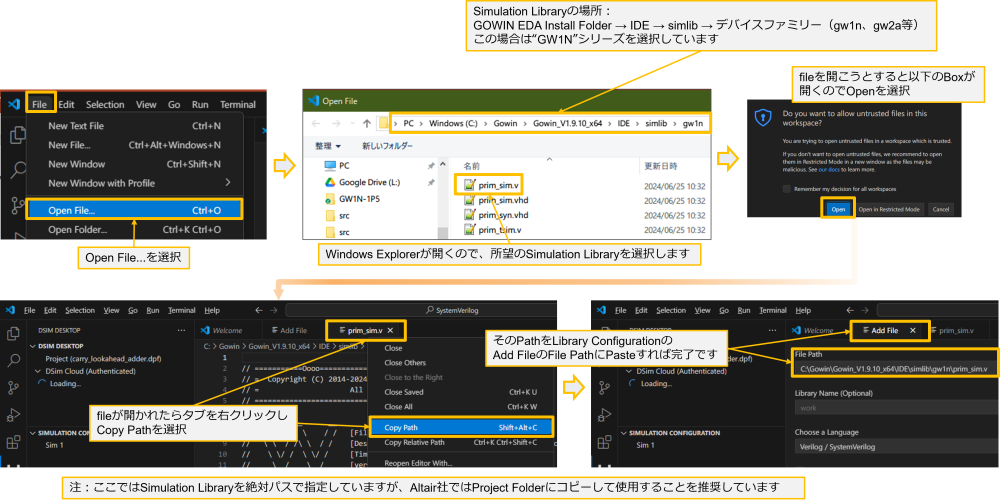

GOWIN Simulation Libraryの登録

GOWIN Simulation Libraryの設定

Library Configurationにて設定します。

GOWIN Simulation Libraryの設定 – 遅延Simulation

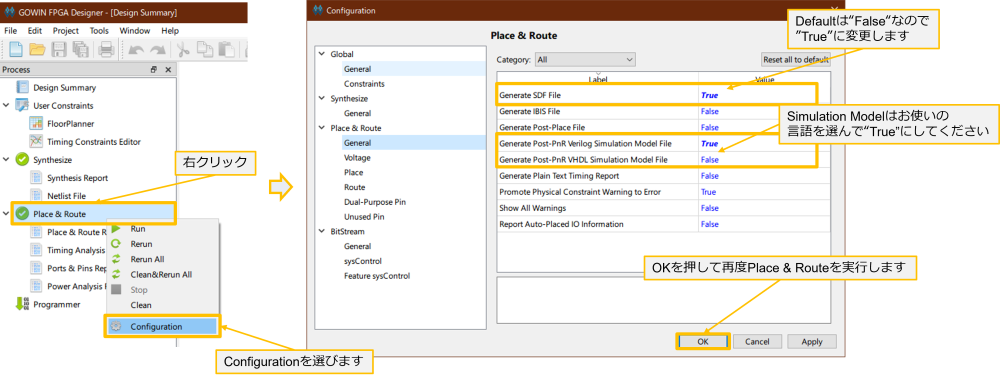

GOWIN EDAにて配置配線を終えた後の遅延Simulation(Timing Simulation)について

遅延Simulationを行うための配置配線後のNetlistおよびSDFの出力方法は以下の通りです。

出力したNetlistとSDFの読み込み

論理Simulation時に読み込んだPrimitive Libraryに加えて「prim_tsim.v」も読み込みます。

NetlistとSDFの組み込み

NetlistとSDFは以下の場所に出力されます。

- Netlist:Project Folder\impl\pnr\project.vo

- SDF: Project Folder\impl\pnr\project.sdf

NetlistはLibrary Configurationに登録し、Compileしてください。

SDFは“$sdf_annotete”にてTestbenchに組み込んでください。

- 例

資料ダウンロード

ここまで、Web記事「GOWIN_EDA_DSim Studio_InstallからSimulationまで」で説明しきれなかった内容を補足資料としてまとめました。ダウンロード用資料もございますので、DSim StudioにてSimulationを行いたい方は、下記Linkより資料のダウンロードをお願いします。