GOWIN FPGA QuestaSim Base活用法

この記事では、特にFPGA開発において、業界標準として広く知られているシーメンス社製「Modelsim」の後継機種である「QuestaSim Base」でのSimulation方法についてご紹介します。GOWINセミコンダクター社(以下GOWIN)のOfficial Simulatorとしては、Altair Engineering社の「DSim Studio」が採用されています。このSimulatorについてはこちらで紹介しておりますので、あわせてお読みいただけますと幸いです。

QuestaSim BaseとModelsimの相違点

シーメンス社の論理シミュレータであるQuestaSim Baseは、ModelSimの上位に位置する後継機種であり、より大規模で複雑な設計の検証に対応できるように機能と性能が強化されています。

QuestaSim Baseでの使い方は、基本的にはModelSimと同じです。ここではGOWIN FPGAのHard IP/Soft IPを使用した際のSimulation方法を記載していきます。

GOWIN FPGAのPrimitive cellを使用してSimulationを行う場合は、下記のFolderよりコピーしてお使いください。

- GW1Nファミリー

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw1n

- GW2Aファミリー

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw2a

- GW5Aファミリー

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw5a

注:インストールフォルダはDefaultでは以下になります

C:¥Gowin

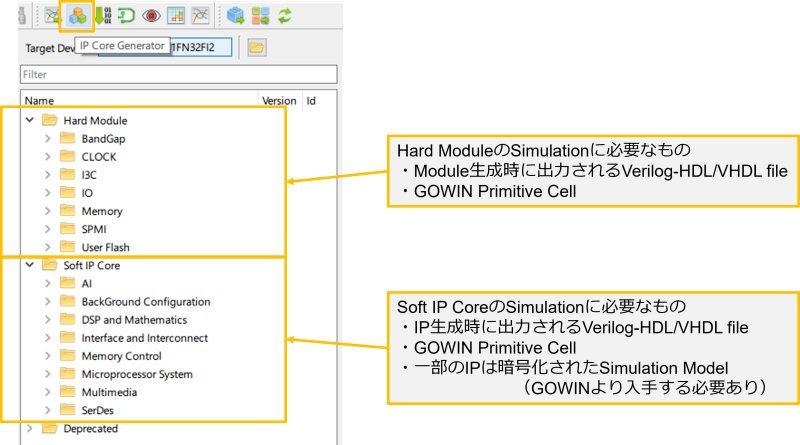

IP Core Generator

GOWINのHard Module、Soft Core IPは、GOWIN EDAのIP Core Generatorで生成します。

Hard IPのSimulation

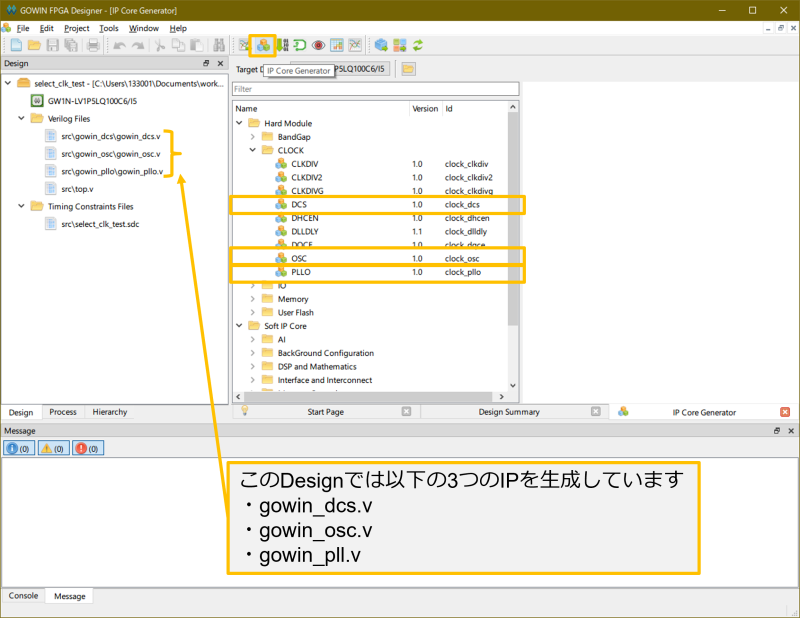

この例では、GOWIN EDA ToolのIP Core Generatorで生成した、DCS(Dynamic Clock Selector)、OSC(On Chip Oscillator)、PLLについてSimulationします。

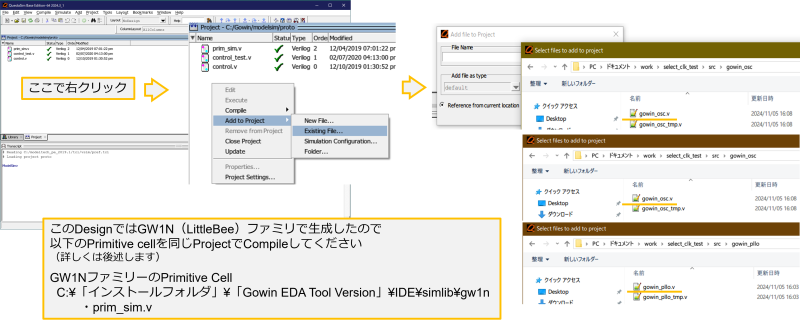

Add to Project → Existing FileでIPを追加します。

-

nIP Core Generatorで生成したModuleはここに出力されます→ ¥¥gowin project folder¥src¥生成IP¥生成IP.v(.vhd)

(VerilogかVHDLはIP生成時に決めることができます)

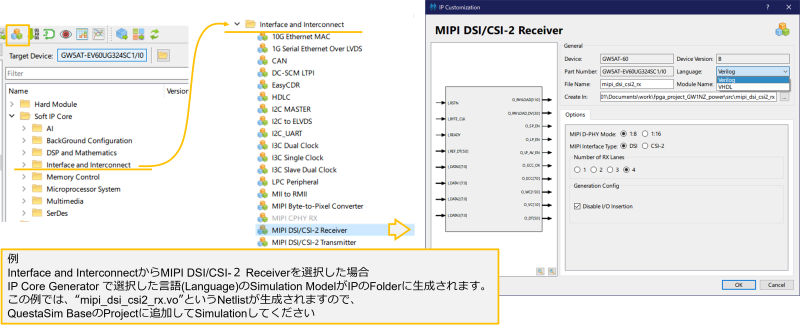

Soft IP Core ModuleのSimulation

Soft IP Coreも基本的にはHard IPと同様の手順でSimulationが可能です。

暗号化されたModuleのSimulation

2025年6月現在以下のIP ModuleはGOWINから入手する必要があります。

■Hard MIPI D-PHY for GW1N-2 and GW5Ax series

■Hard MIPI C-PHY for GW5AT series

■ADC for GW5Ax series

■High-Speed Transceiver for GW5AxT series

- GOWIN High-Speed Transceiver(SerDes IP)は、GOWIN SerDesをベースとした包括的なIPです。シリアルイーサネット、CPRI、JESD204B、PCIeなど、さまざまな高速プロトコルが含まれています。また、GOWIN SerDesを柔軟に構成するためのカスタマイズPHYも提供します。

- プロトコルのリストは以下の通りです:

・BCDR

・1G, 2.5G, 10G Serial Ethernet

・QSGMII

・RoraLink 64B66B/RoraLink 8B10B

・CPRI

・JESD204B

・Serial RapidIO

・USB 3.0 PHY

・USB 3.1 PHY

・EDP PHY

・SDI PHY

・SLVS-EC RX

・Customized PHY

・PCI Express Controller

暗号化されたIP Moduleはそれぞれ対応するSimulator向けに提供されます。

ご用命の際はお使いのSimulatorをご指定ください。

GOWINにて対応しているSimulatorは以下の通りです。

- Modelsim(QuestaSim):Siemense

- VCS:Synopsys

- Xcelium:Cadence

Primitive Libraryの追加

Simulation Libraryの追加

- GOWINのIPを使用している場合やIP Core Generatorで生成したIPのSimulationには、Simulation用 Library fileをCompileしておく必要があります。

- Library file名:prim_sim.v

Libraryの場所

-

GW1N

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw1n

-

GW2A

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw2a

-

GW5A

C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\gw5a

FPGAにマッピング後のTiming Simulationには以下のfileを用います。

- Timing Simulation用Library file名:prim_tsim.v

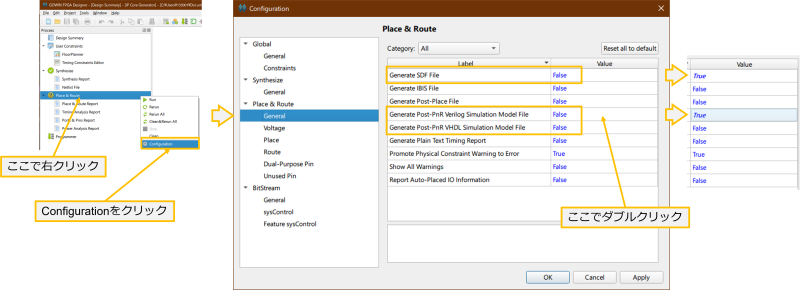

Timing Simulation

EDAからNetlistとSDFを生成することで、FPGAにマッピング後のTiming Simulationを行うことができます。

- Verilogであれば*.vo、VHDLでは*.vhoのNetlistが生成されます。

- Timing Simulation用Libraryfile:prim_tsim.vと一緒にQuestaSim BaseのProjectに追加してください。

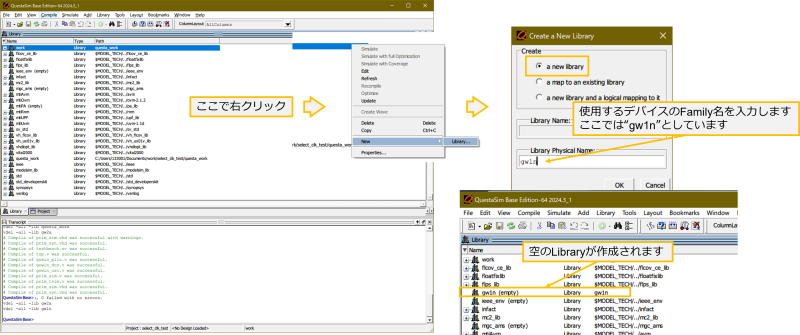

VHDL Simulation用Libraryの追加

VHDLのSimulationにはprimitive cellをLibrary化する必要があります。

- VHDL用Simulation Libraryは以下にあります。

- C:¥「インストールフォルダ」\「Gowin EDA Tool Version」\IDE\simlib\Family

- GOWIN FPGA Familyは2025年6月現在下記3種があります。

gw1n:Little Bee family

gw2a:Arora family

gw5a:Arora V family

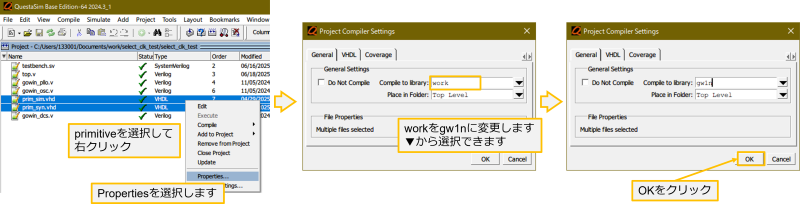

- VHDL Library化するprimitive Libraryは以下の2種です。

prim_sim.vhd

prim_syn.vhd

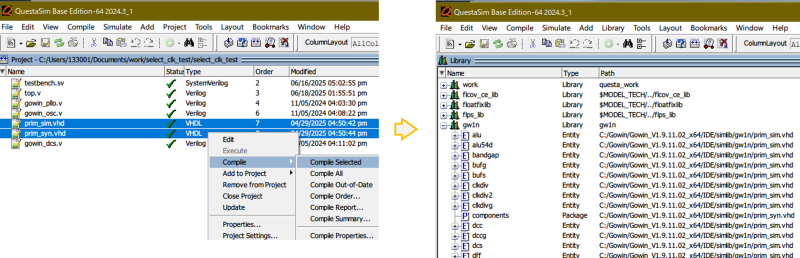

GUIからのLibrary追加

空のLibraryが作成されたので、primitiveをCompileして使用可能にします。

Library化の完成です。

QuestaSim BaseのTranscriptからコマンド入力でLibrary化する方法もあります。

- QuestaSim Base> vlib “Family“

- QuestaSim Base> vcom -2008 -work “Family“ ”C:¥「インストールフォルダ」¥「Gowin EDA Tool Version」¥IDE¥simlib¥”Family“¥prim_sim.vhd”

- QuestaSim Base> vcom -2008 -work “Family“ ” C:¥「インストールフォルダ」¥「Gowin EDA Tool Version」¥IDE¥simlib¥”Family”¥prim_syn.vhd“

例:gw1nファミリでLibrary化する場合

- QuestaSim Base> vlib gw1n

- QuestaSim Base> vcom -2008 -work gw1n “C:/Gowin/Gowin_V1.9.11.02_x64/IDE/simlib/gw1n/prim_sim.vhd”

- QuestaSim Base> vcom -2008 -work gw1n “C:/Gowin/Gowin_V1.9.11.02_x64/IDE/simlib/gw1n/prim_syn.vhd“

注:GOWIN Primitive CellをGOWINインストールフォルダからProject用work folderにコピーしている場合は、file pathにお気を付けください

GOWIN FPGA QuestaSim Base活用法

ここまでで、GOWIN FPGA QuestaSim Base 活用法の説明は終了です。この記事では、GOWIN IPのSimulation方法に特化して解説しました。今回の内容と合わせて、IPを使用しない通常のSimulation方法をまとめた資料は、下記のリンクよりダウンロードできます。