商品基礎情報

MIPI とは?

MIPIとは、Mobile Industry Processor Interface の略で 、スマートフォン、タブレット、ラップトップなどのモバイル機器のインターフェースに関する標準規格が定義されています。 MIPI はビジネス アライアンスである MIPI Alliance によって開発され管理されています。

GOWINセミコンダクター社は MIPI Alliance のメンバーに加入しています。

従来、MIPI はモバイルアプリケーションでの用途が想定されていましたが、高解像度のイメージ センサーやディスプレイが AI、IoT、自動車、産業機器、医療機器に導入されるケースが増えるにつれ、MIPI への関心はモバイルアプリケーションに限らず広がってきています。

MIPIスタンダードでは、MIPI D-PHY、C-PHY、M-PHY®、および A-PHY® の 4 つの固有の物理 (PHY) 層仕様を定義しています。

GOWIN MIPI PHY ソリューションの概要

GOWINセミコンダクター社は 既に量産されている LittleBee (GW1Nx) および、Arora (GW2Ax) デバイスの両方で、MIPI D-PHYソリューションを提供しています。

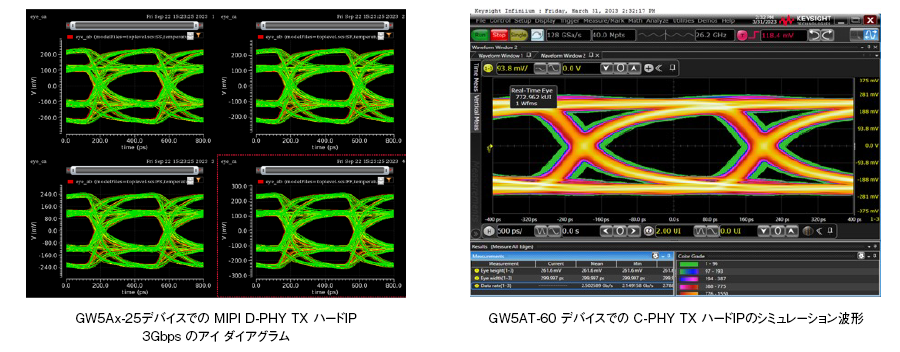

特に、新しい製品である Arora-V ファミリ FPGA (GW5Ax) は MIPI C-PHY ハードIPをサポートしたFPGAです。

以下は GOWIN FPGAがサポートするMIPI PHY (ソフト/ハード)の仕様概要です。

| デバイス | タイプ | D-PHY RX | D-PHY TX | C-PHY RX | C-PHY TX | 備考 |

| GW1Nx | ソフトIP |

最大 1.2Gbps |

最大 1.2Gbps |

ー | ー |

Max at C7 speed grade or above |

| ハードIP |

GW1N-LV2 のみ |

ー | ー | ー |

1-Core w/4-Lanes(RXのみ) |

|

|

GW2Ax |

ソフトIP |

最大 1.2Gbps |

最大 1.2Gbps |

ー | ー |

|

| ハードIP |

– |

ー | ー | ー |

|

|

|

GW5Ax 138K/75K |

ソフトIP | 最大 1.5Gbps | 最大 1.6Gbps | ー | ー | |

| ハードIP |

最大 2.5Gbps |

ー | ー | ー |

2-Core w/4-Lanes each (RXのみ) |

|

|

GW5Ax 25K |

ソフトIP |

最大 1.6Gbps |

最大 2.0Gbps |

ー | ー | |

| ハードIP |

最大 2.5Gbps |

最大 2.5Gbps |

ー | ー |

1-Core w/4-Lanes (RXまたはTX) |

|

|

GW5AT 60K/15K |

ソフトIP |

最大 1.6Gbps |

最大 2.0Gbps |

ー | ー | |

| ハードIP |

最大 2.5Gbps |

最大 2.5Gbps |

最大 2.5Gsps |

最大 2.5Gsps |

D-PHY 1-Core w/4-Lanes (RXまたはTX) C-PHY 1-Core w/3-Trios (RXまたはTX) |

※ここでの数値は、今後のGOWINセミコンダクター社内での特性評価によって更新される可能性があります。

MIPI PHY ハードIP

GOWINセミコンダクター社は、GW1N-LV2 デバイスで最初の MIPI D-PHY RX ハードIPを開発しました。

この IPコアは MIPI D-PHY 仕様 V1.1 に準拠しており、最大受信データ レートは 1.5Gbps です。

Arora V FPGA ファミリでは、2.5Gbps の D-PHY V1.2 と 2.5Gsps(5.7Gbps) の C-PHY V1.1 の両方のハードIPを開発しました。

詳細な機能を次の表に示します。

| 主な機能 | GW5Ax-138 | GW5Ax-75K | GW5AT-60 | GW5Ax-25 | GW5AT-15 |

| MIPI D-PHY RX/TX、デスキュー機能付き | RX のみ | RX のみ | ✔ | ✔ | ✔ |

| SoT HS-Sync によるレシーバーイコライゼーション、ワードおよびレーンアライメント | ✔ | ✔ | ✔ | ✔ | ✔ |

| 一般的なソースシンクロナス高速インターフェースとして構成可能なPHY | ✔ | ✔ | ✔ | ✔ | ✔ |

| D-PHY の RX/TX パッド共有、4 データ レーン、レーンベースの構成モード | RX のみ | RX のみ | ✔ | ✔ | ✔ |

| MIPI C-PHY RX/TX パッド共有、最大 3Gsps、3トリオ | n/a | n/a | ✔ | n/a | ✔ |

GPIO ベースの MIPI ソフトPHY IP

GOWIN FPGA のプログラマブル IO (GPIO) は、外部受動抵抗ネットワークを利用してMIPIインターフェースをエミュレートできます。

GPIO ベースの MIPI ソフトPHY ソリューションを使用する大きな利点は、インターフェース実装の柔軟性です。

例えば、VR やドローン システムでは、入力として複数のカメラが必要となり、データが1つの出力に集約される場合があります。

昨今のSoCの中で、このような要件に対応できるものはほとんどありません。

MIPI D-PHY ソフト IP

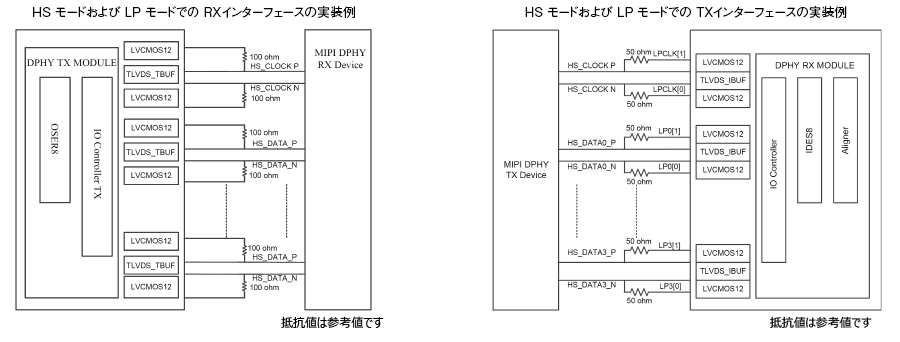

下図は GPIO を使用して MIPI インターフェースをエミュレートするための受動抵抗ネットワークの実装例を示しています。

最大のパフォーマンスを達成するには、配線と信号の整合性をとることが非常に重要です。

GOWIN MIPI PHY 及び、プロトコル層の IPとリファレンス デザイン

GOWINセミコンダクター社は、GOWIN EDA の IPコア ジェネレーターを通じて、多くの PHY IP に加え、MIPI CSI-2 や MIPI DSI などのプロトコル層のソフトIP を提供します。

次の表は現在利用可能な IPのドキュメント/リファレンスデザインの一覧になります。

| IP | タイプ | ドキュメント リンク |

| Gowin GW1N-2 Hardened MIPI D-PHY RX |

ハードIP |

GOWIN社Web |

| Arora V Hardened MIPI D-PHY User Guide | ハードIP | GOWIN社Web(pdf) |

| Gowin Hardened MIPI C-PHY User Guide | ハードIP | GOWIN社Web(pdf) |

| Gowin MIPI RX Advance | ソフトIP | GOWIN社Webページ |

| Gowin MIPI TX Advance | ソフトIP | GOWIN社Webページ |

| Gowin MIPI DSI/CSI-2 Transmitter | ソフトIP | GOWIN社Webページ |

| Gowin MIPI DSI/CSI-2 Receiver | ソフトIP | GOWIN社Webページ |

| Gowin MIPI Pixel-to-Byte Converter | ソフトIP | GOWIN社Webページ |

| Gowin MIPI Byte-to-Pixel Converter | ソフトIP | GOWIN社Webページ |

GOWINセミコンダクター社の MIPI ハードコアIPは最適化された確かな性能を提供し、ソフトコアIPはFPGAのプログラマビリティを活用して多様なアプリケーションのニーズに適合する比類のない柔軟性を提供します。